## Overload Circuitry Protects Batteries and Power Supplies

A combination of current-sense amplifier, dual-comparator and external CMOS switches can be used to prevent the damaging effects of a reversed-polarity battery or short-circuit load.

The most widely used device for overcurrent protection is a simple fuse. High current due to an overload heats the fusible metallic link, causing it to melt and open the circuit. The fuse is simple and economical. However, fuses' relatively long reaction time, high resistance, and need for replacement make them impractical for some applications.

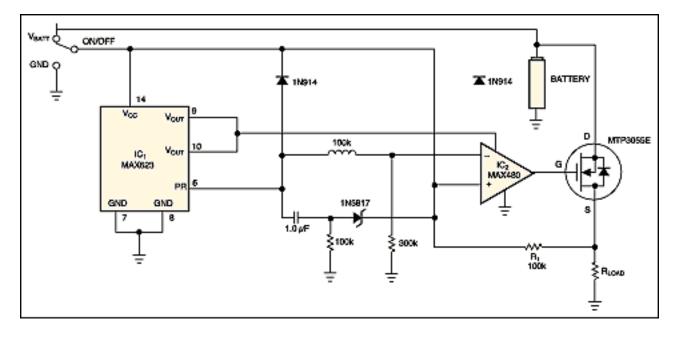

A logic-controlled switch can provide low-loss switching and low quiescent current in addition to output short-circuit protection (Figure 1). The regulated charge pump (IC<sub>1</sub>) generates a gate drive of  $V_{BATT}$ +10V for the NMOS FET switch, Q<sub>1</sub>. You turn on the circuit by applying  $V_{BATT}$  to the on/off input.  $V_{OUT}$  (pins 9 and 10) then pumps up to ( $V_{BATT}$ +10V) within a millisecond or so, providing power to the op amp (IC<sub>2</sub>). To ensure that Q<sub>1</sub> remains off until sufficient gate drive is available, a threshold detector in IC<sub>1</sub> triggers a 0V-to- $V_{BATT}$  transition at the PR terminal (pin 6 of IC<sub>1</sub>) when the rising output equals  $V_{CC}$ +8V.

Figure 1. This logic-controlled switch circuit provides short-circuit protection at R<sub>LOAD</sub>.

The appearance of V<sub>BATT</sub> at the PR terminal produces 0.75· V<sub>BATT</sub> at the op amp's inverting input and a 100msec pulse at the noninverting input. The pulse kicks  $Q_1$  into conduction, and  $Q_1$  stays on as long as the source voltage remains more positive than the op amp's inverting input. Feedback through  $R_1$  provides short-circuit protection. If high load current pulls the source voltage below the reference level at the inverting input, the gate drive goes low and turns off  $Q_1$ . The collapsing load voltage then latches off the switch. To reset, pull the on/off input to ground for at least 100msec and then back to  $V_{BATT}$ .

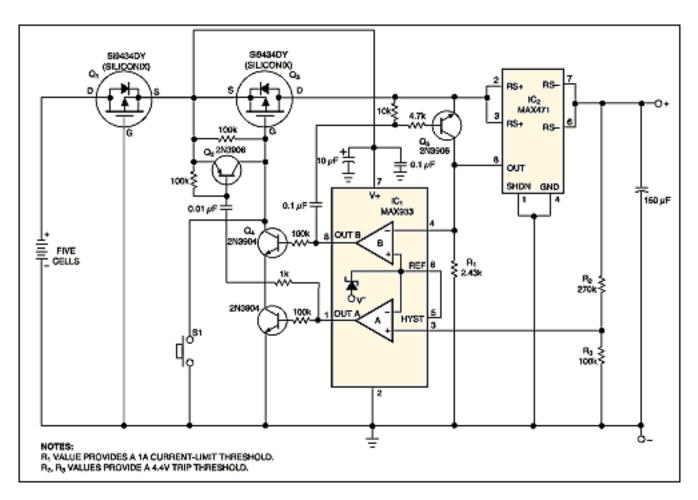

In the circuit in Figure 2, one PMOS FET,  $Q_1$ , provides passive protection against battery reversal, and a second MOSFET,  $Q_3$ , disconnects the load from the battery in the event of excessive forward current flow. You should orient the MOSFETs' body diodes to prevent current flow when either device is off, regardless of the battery polarity.

Figure 2. This circuit blocks the effect of a reversed-polarity battery or short-circuited load.  $R_1$  sets the current-limit threshold.

$Q_1$ , for example, connects backward (with respect to conventional practice) to align its body diode in the direction of normal current flow. A properly installed battery pulls  $Q_1$ 's gate more than 5V below its source, turning on  $Q_1$ . A reversed battery drags the gate above the source,

blocking current flow by reverse-biasing the body diode.

The current-sense amplifier, IC<sub>2</sub>, produces a small output current at pin 8 that is proportional to the current flowing between the RS+ and RS- terminals. The resulting voltage across R<sub>1</sub> controls comparator B in IC<sub>1</sub>. During normal operation, Q<sub>3</sub> remains on, because both comparator outputs are high. When the load current causes sufficient voltage across R<sub>1</sub> to trip the B comparator, Q<sub>3</sub> turns off and disconnects the battery from the load. At the same time, Q<sub>5</sub> pulls the B comparator's inverting input to the supply rail, latching Q<sub>3</sub> off as the supply rail falls. Q<sub>2</sub> speeds the turn-off of Q<sub>3</sub>.

Comparator A acts as a safety valve that turns off  $Q_3$  in the event of a rapid short circuit. (In the absence of  $Q_3$ , a short circuit causes oscillation: The initial increase in load current drives  $Q_4$  on and  $Q_3$  off, and the resulting loss of supply voltage kills IC<sub>2</sub>, allowing  $Q_3$  to turn on again.) R<sub>1</sub> sets the current limit at 0A to 3A, according to the following equation, where 2000 is a gain factor internal to IC<sub>2</sub>, and V<sub>TH</sub> is the threshold of the comparators in IC<sub>1</sub>:

$I_{LIMIT} = 2000 \cdot V_{TH}/R1.$

A similar version of this article appeared in the March 1, 1996 issue of EDN.

## **More Information**

MAX471: <u>QuickView</u> -- <u>Full (PDF) Data Sheet</u> -- <u>Free Samples</u> MAX933: <u>QuickView</u> -- <u>Full (PDF) Data Sheet</u> -- <u>Free Samples</u>